?DS852之間數字8率合成圖片器(DDS)更換AD9858/AD9851

發布了時刻:2025-03-31 15:28:11 &n�������bsp; 閱讀:574

DS852直接性數值率合并器(DDS)與亞德諾半導體設備(ADI)的AD9858/AD9851在性能指標指標、軟件情況、人工成本及提供鏈等領域的綜合十分,是考慮可否來進行編輯的關鍵點緣由。

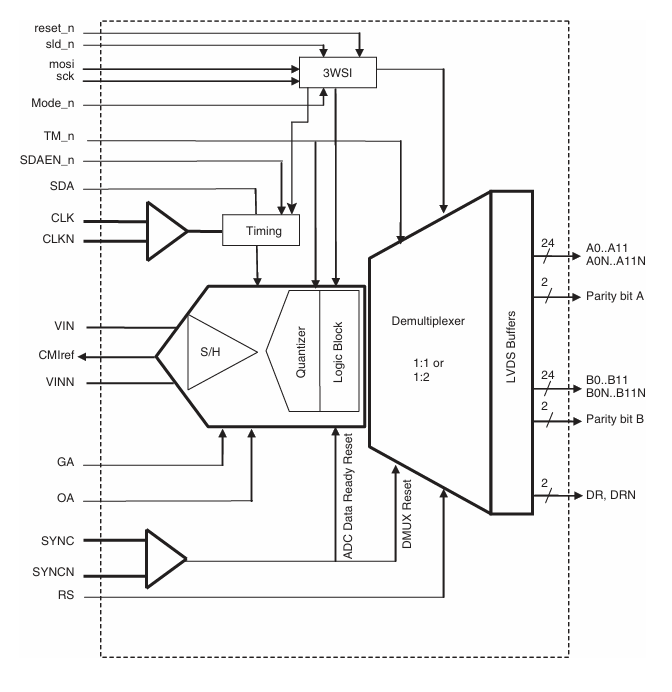

AD9858:

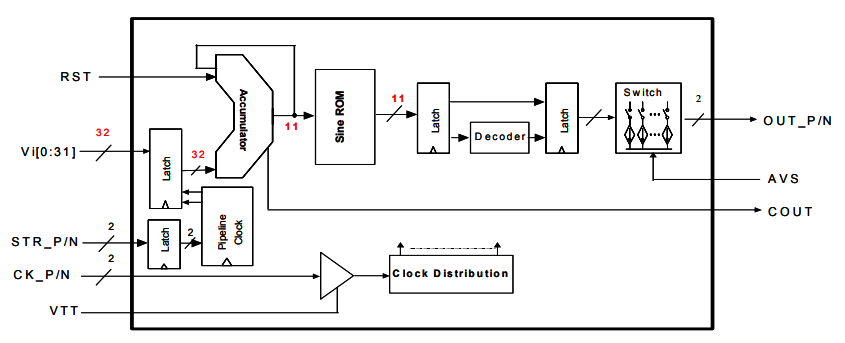

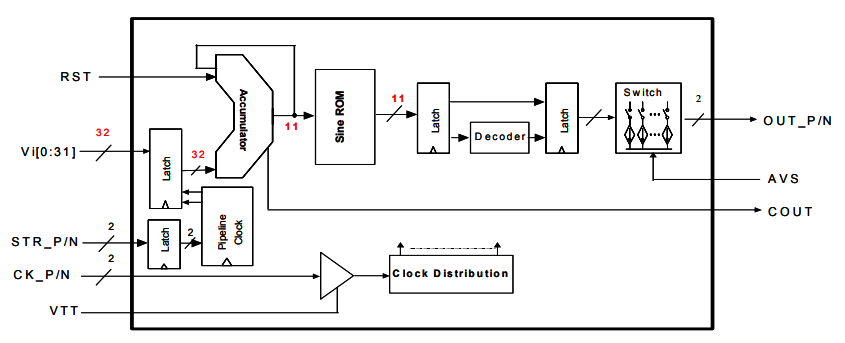

以它優良(liang)的(de)(de)安全性(xing)能(neng)����實現自(zi)我價值:具有1Gsps的(de)(de)內部(bu)數(shu)字時(shi)鐘(zhong)車速,要接受最高的(de)(de)人(ren)達2GHz的(de)(de)顯示石(shi)英鐘(zhong)(待選2分頻),并集(ji)變為(wei)了(le)10位(wei)DAC。其(qi)相位(wei)噪音和無雜散動態數(shu)據(ju)時(shi)間(jian)范圍的(de)(de)表(biao)現非常出色,配(pei)(pei)有了(le)32位(wei)可和程序(xu)編寫(xie)聲音頻率寄存(cun)器(qi),簡化版了(le)操作(zuo)的(de)(de),作(zuo)為(wei)了(le)8位(wei)并行傳輸和SPI串行掌握標準接口。不僅而且,AD9858還幫助自(zi)主掃頻效果,內裝置4種次數(shu)配(pei)(pei)資文件資料�����,利用(yong)3.3V主機電(dian)源輸電(dian),典型的(de)(de)功耗測試為(wei)2W。它還集(ji)成為(wei)可編學習電(dian)勢泵、相位(wei)頻帶寬度加(jia)(jia)測器(qi)與(yu)加(jia)(jia)快(kuai)確定控(kong)制電(dian)路(lu),進一大步加(jia)(jia)強了(le)其(qi)效果。

與DS852������想必,若DS852相同(tong)擁有(you)著(zhu)(zhu)相同(tong)的飛速掛(gua)鐘穩定性,擁有(you)著(zhu)(zhu)很好的相位躁音和(he)無雜(za)散信息(xi)范(fan)圍(wei)之內,和(he)在(zai)制造費、表(biao)面(mian)積、輸(shu)出功率(lv)等(deng)等(deng)方面(mian)展現什么出比較突出優劣勢,和(he)當軟(ruan)件(jian)對(dui)掃頻技能(neng)、頻繁配置單zip文件(jian)等(deng�������)基本特征供需不(bu)須嚴格時,DS852可變(bian)為AD9858的使(shi)用進行。十分是(shi)DS852在(zai)能(neng)耗(hao)層面(mian)主要(yao)表(biao)現更加,更適宜于能(neng)耗(hao)靈敏的輕便式式設配或電(dian)池板電(dian)力設配,這樣特別(bie)使(shi)其在(zai)當前廣泛應用游戲場(chang)景中更加具備(bei)吸(xi)引女生力。

性能(neng)因素因素

主(zhu)要參數/型號查詢 | DS852 | AD9858 |

頻次調諧辨(bian)別率 | 32位 | 32位(可java開發(fa)規律(lv)寄(ji)存(cun)器) |

波幅分(fen)別(bie)率 | 11位 | - |

鬧鐘(zhong)速率 | 會達2.5 GHz | 高2 GHz(鍵(jian)盤輸(shu)入石英(ying)鐘,供選擇二分頻) |

余弦波轉為學習能(neng)力 | 在2.2 GHz數字(zi)時鐘速���率下,能轉換(huan)表示1.1 GHz的正(zh�������eng)弦函數波 | 可以出現比較高400+ MHz的次數(shu)捷變模以打出正弦(xian)交流電波(bo) |

把(ba)控好方法(fa) | 可確認(ren)微控(kong)住器或DSPIC芯片通過隨時控(kong)制 | 并行(xing)執行(xing)或串(chuan)行(xing)彈(da�������n)出格(ge)式文������(wen)件調節(jie) |

輸(shu)入(ru)性能指標 | 帶(dai)50Ω側(ce)面終商品詳(xiang)情頁專一性模擬機波型內(nei)容輸出 | - |

SFDR(無雜(za)散(san)情況范(fan)圍(wei)之內) | 很差不小于50 dBc | 經驗豐富(實際(ji)的數據(ju)可以因采用而異) |

工作電(dian)壓(ya) | 單獨-5.0V24v電源的(de)功能消耗(hao)為(wei)3.0W | 2W(主要值) |

封口主要形式(shi) | 64針QFN封裝類型(xing) | TQFP-100封口 |

AD9851:

效果指標(biao)(biao)部(bu)分(fen)(fen),AD9851內置了可(ke)(ke)代碼編程的(de)(de)(de)直接的(de)(de)(de)小(xiao)數速(su)率(lv)分(fen)(fen)解成(cheng)(DDS)設備、高(gao)耐(nai)腐蝕性數模(mo)轉成(cheng)器(qi)(DAC)與(yu)(yu)高(gao)速(su)公路相(xiang)(xiang)比器(qi)。僅(jin)憑32位(wei)的(de)(de)(de)概率(lv)把控好字,在180MHz的(de)(de)������(de)掛鐘速(su)率(lv)下,AD9851要能變(bian)現0.0372Hz的(de)(de)(de)精密細輸出的(de)(de)(de)速(su)率(lv)分(fen)(fen)辯率(lv)。于外部(bu)融合的(de)(de)(de)6倍頻(pin)REFCLK倍頻(pin)器(qi),允許的(de)(de)(de)外接低(di)頻(pin)基準線掛鐘,借以添加(jia)180MHz的(de)(de)(de)里(li)面(mian)標(biao)(biao)準數字時鐘,彰(zhang)顯出優勝的(de)(de)(de)無雜散(san)動圖依據和相(xiang)(xiang)位(wei)燥音特點(dian)。與(yu)(yu)此(ci)同時,AD9851還供應了5位(wei)的(de)(de)(de)可(ke)(ke)java開(kai)發(fa)相(xiang)(xiang)位(wei)�����調(diao)變(bian)計(ji)算精度,確(que)定所在正(zheng)弦波形(xing)的(de)(de)(de)相(xiang)(xiang)位(wei)偏離(li)乘以11.25度。

與(yu)DS852對比,若DS852在頻(pin)帶寬度(du)(du)分辯(bian)率、相位調制(zhi)解調精準度(du)(du)等(deng)主(zhu)導指標里能夠滿(man)足(zu)是需(xu)要(yao)某(mou)一(yi)用的(de)(de)(de)(de)意愿,也(ye)許(xu)在的(de)(de)(de)(de)成(cheng)本有效控制(zhi)、體(ti)積計算改進等(deng)個方面(mian)(mian)蘊含著更應(ying)(ying)該(gai)嚴格(ge)耍求(qiu)(qiu)的(de)(de)(de)(de)耍求(qiu)(qiu),也(ye)許(xu)是需(xu)要(yao)更應(ying)(ying)該(gai)靈活性各(ge)樣的(de)(de)(de)(de)音(yin)頻(pin)接口辦法,那DS852無疑是不(bu)是個直得(de)顧慮的(de)(de)(de)(de)使用界面(mian)(mian)。比如說,當DS852彰顯(xian)出越來越高的(de)(de)(de)(de)集成(cheng)式度(du)(du),就能在非常緊湊型的(de)(de)(de)(de)區域內(�������nei)實現了與(yu)AD9851特別(bie)的(de)(de)(de)(de)功能鍵,亦(yi)或是其插口制(zhi)定更加的(de)(de)(de)(de)更加方便(bian)與(yu)系統(tong)中(zhong)的(de)(de)(de)(de)另一(yi)個基(ji)帶芯片(pian)參與(yu)無縫拼接連(lian)接方式時(shi),DS852便(bian)變成(cheng)了一(yi)家最能體(ti)現引起力的(de)(de)(de)(de)的(de)(de)(de)(de)選擇(ze)。

性能方面性能

技術(shu)參(can)數(shu)(shu)/技術(shu)參(can)數(shu)(shu) | DS852 | AD9851 |

頻帶寬度調諧判別(bie)率 | 32位 | 32位(采用32位頻繁(fan) 有效控(kong)制字進行) |

秒表次(ci)數(shu) | 相(xiang)當于(yu)2.5 GHz | 較高180 MHz(整體鐘表) |

正(zheng)弦交流電(dian)波(bo)繪制作用(yong) | 在2.2 GHz鐘(zhong)表速率(l�����v)下,能制(zhi)成相似(si)1.1 GHz的(de)余弦波 | 在180 MHz鬧鐘下,的輸(shu)出率鑒別率較高 |

相位調(diao)配計算精(jing)度(du) | - | 5位(wei)(可確保輸出精度(du)波型的相(xiang)位(wei)偏(pian)離不(bu)低������于11.25度(du)) |

調節具體方法(fa) | 可可以通過微驅動(dong)器或(huo)DSP單片機芯片完���成及時有(you)效(xiao)控制(zhi) | 并行執行或串(chuan)行異步啟動格(ge)試 |

導出因素 | 帶50Ω后面終端互補式摸擬波(bo)形(xing)參數工作輸出 | 內外(wai)部高較器可將余弦(xian)波(bo)變換(huan)為(wei)方(fang)波(bo)輸(shu�������)送 |

SFDR(無雜散動向使用范圍) | 較差(cha)高(gao)于50 dBc | 好點(dian)(按照(zhao)目標值可以因采用而(er)異) |

耗電量(liang) | 單一個-5.0V電的功耗測試為3.0W | 在3.3V輸電(dian)時,耗電(dian)量為155mW(或650mW,按(an)照(zhao)其具(ju)體的參(can)數和狀況已經(ji�������ng)有點有差異) |

打包封(feng)裝風格 | 64針QFN封裝形(xing)式 | 超家庭型(xing)28引腳SSOP裝封 |

西安市立維創展科技信息是EUVIS的代理(li)權銷售(shou)商,最(zui)主(zhu)要帶來EUVIS的國內領先的高速的數模改換DAC、簡單號碼(ma)頻段提煉(lian)器DDS、重復使用DAC的集成�������ic級服(fu)務,與快速采(cai)集器板卡、動態展示(shi)弧形造(zao)成器等服(fu)務,原裝進口期貨,產品報(bao)價優(you)點,喜愛管理(li)咨詢(xun)。

英文版

英文版

產業信息

產業信息