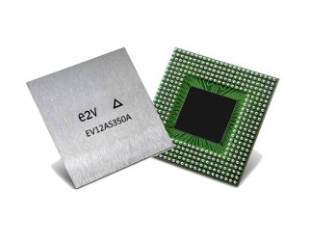

AT84AS004整合了10位2 Gsps齒條參數變為器和1:4 DMUX,設計構思使用獨一或2、奈奎斯特區聯通寬帶表現的精密小數化。它的特征是7.8有效地2 Gsps時的五位數(ENOB)和–55 dBFS無雜散的動態標準(SFDR)獨某個奈奎斯特區和7.5位,在2、個奈奎斯特上長53分貝的SFDR。1:4多路小數傷害與LVDS規律兼容,于與標準界面FPGA或DSP。AT84AS004的最快開機運行訪問速度為2 GSP。AT84AS004用到25×35毫米(mm)EBGA317芯片封裝。此包的TCE與FR4想同板,在深受大的熱突破時打造挺不錯的靠譜性。

邀請來北京市立維創展信息技術有限的我司中國官方小程序小程序!

-

亚洲一区二区三区在线-欧美一二区-欧美亚洲一区-欧美激情一区

Home -

關于我們

About -

微波元器件

Microwave- AMCOM

- CUSTOM MMIC

- RF-LAMBDA

- QORVO

- MACOM

- SOUTHWEST

- NOVA射頻微波

- KRYTAR

- Aeroflex-API Tech

- Anaren

- Anritsu

- RADITEK

- North Hills

- Synergy微波

- WENTEQ

- MITEQ

- Marki

- RF-Labs

- ADI

- CREE

- UMS微波

- PULSAR微波

- MegaPhase

- JDSU光纖測試

- AMG-Microwave

- Ironwood

- Teledyne防務電子

- HEROTEK

- ARRA

- MCLI

- Leadway

- CERNEX

- Mi-Wave

- ATM Microwave(L-3)

- UTE Microwave

- NEL Frequency Controls

- API SAW Oscillators

- SemiGen

- KR Electronics

- MECA

- Electro-Photonics

- RLC Electronics

- JUPITER(Canada)

- ?IPP

-

電源模塊

Power -

DAC | ADC芯片

DAC|ADC -

微處理器

MCU -

風扇

Fan -

熱縮管

Heat Shrink Tubing -

自研產品

Leadway Prodcuts - 聯系我們

Contact

漢語

漢語

DACADC集成塊

DACADC集成塊